Menu

Rechercher

Accueil > Équipes Techniques > Electronique et Instrumentation > Electronique Back-End SciFi LHCb > Electronique du trajectographe à fibres scintillantes ( SciFi Tracker ) pour l’expérience LHCb

Electronique du trajectographe à fibres scintillantes ( SciFi Tracker ) pour l’expérience LHCb

Implication technique du LPNHE

par Jean-Luc MEUNIER, Olivier Le Dortz - 18 mai 2022

Complément au poster composé à l’occasion de la biennale du LPNHE 2022

Dernières nouvelles de l’intégration du SciFi au détecteur LHCb

- l’ensemble des C-frame avec leur électronique frontale est installé en caverne du LHC depuis le 7 Avril 2022.

- Installation de 2 C-Frame en février 2022.

https://lhcb-outreach.web.cern.ch/2022/01/28/installation-of-scifi/

- Installation 1ère C-Frame du SciFi en 2021.

https://home.cern/news/news/experiments/scifi-moment-lhcb-experiment - Vidéo de l’installation de C-Frame dans la caverne.

https://lhcb-media.web.cern.ch/lhcb-media/LS2/Final/LHCb_May-2021-SciFi.mp4

- Montage 1ère C-Frame en 2019

https://home.cern/fr/news/news/experiments/ls2-report-lhcb-looks-future-scifi-detector

Présentation Générale

Le trajectrographe SciFi est constitué de fibres optiques scintillantes en plastique de 2.4m avec un diamètre de 0.250mm. Il intègre 12 couches (C-FRAME) équipées de module de photo-multiplicateurs à silicium (SiPM) de 128 canaux chacun.

Voir le poster suivant :

- Poster général du tracker SciFi

- Poster du SciFi Tracker (journées portes ouvertes 2019 du CERN, Blake Leverington). Il montre le positionnement du trajectographe SciFi au du détecteur LHCb.

Electronique Front-End (FEE)

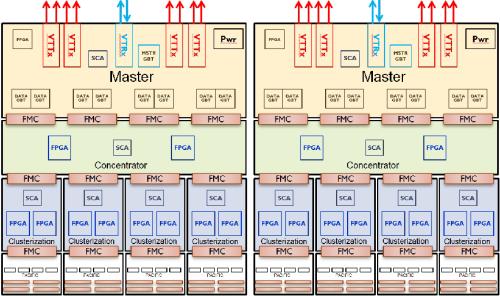

Dans cette section, on décrit le flot de données de la numérisation du signal en sortie de SiPM à la transmission sur un lien GBT (GigaBit Transceiver). La figure suivante présente les différents éléments qui composent la carte front-end.

- ROB electronics boards overview

- source : Nikhef, Wilco Vink

Les impulsions issues des SiPM, sont discriminées et numérisées par des comparateurs à 3 seuils en mots de 2 bits, lesquels sont transférés sur des bus de 32 bits du composant PACIFIC vers les FPGA de Clusterization à 160 Mb/s. Après traitement du FPGA, on obtient des données au format de Cluster (une liste valeurs de 9 bits chacune), lequel définit la position du channel du SiPM qui a contribué à l’évènement. Les données Clusterisées sont étiquetées avec une entête et transférées vers des sérialisers GBT via un bus LVDS de 28 bits. Pour finir, les données, provenant des 8 sérialisers GBT, sont ensuite transmises en série via les convertisseurs optique VTTx .

Electronique Back-End

Carte PCIe40

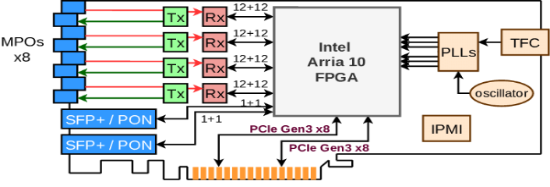

L’électronique back-end de l’upgrade LHCb repose sur un élément central, la carte PCIe40 qui a été conçue et produite par le CPPM.

Elle se compose de :

- 1 FPGA de 1.15 million cells (Arria10 10AX115S3F45E2SG)

- 48 liens bidirectionnels fonctionnant jusqu’à 10 Gbits/s (minipods)

- 2 liens bidirectionnels fonctionnant jusqu’à 10 Gbits/s pour la distribution d’horloge

- 1 interface PCIexpress pouvant atteindre un taux de 112 Gbit/s

- Diagramme de la carte PCIe40

- source CPPM

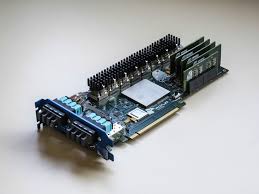

- PCIe40

- source CPPM

Configuration LHCb

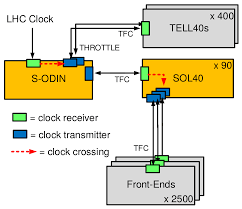

Le FPGA de la carte PCIe40 permet d’adapter celle-ci à différentes fonctionnalités spécifiques du détecteur. Pour LHCb, la carte est déclinée en 3 versions :

- SODIN qui est en charge de la supervision générale et de la distribution temporelle du détecteur.

- SOL40 qui gère le slow-control du détecteur et la distribution des signaux rapides aux sous-élements front-end et back-end ( TFC=Trigger and Fast Control )

- TELL40 qui recueille les données de plusieurs cartes front-end pour en fabriquer des fragments d’évènement.

L’image suivante montre de quelle manière l’horloge du LHC est distribuée par SODIN vers SOL40 et TELL40s.

- Illustration of the clock distribution paths in the upgraded LHCb readout architecture

- source CERN

TELL40 pour SciFi

Le LPNHE a pris en charge le développement de firmwares spécifiques pour les TELL40s du sous-détecteur SciFi.

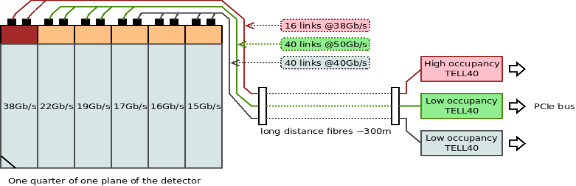

- Structure d’une C-Frame

Le « beam » du LHC se situe au centre du détecteur LHCb. En conséquence, les régions les plus proches du « beam » ont un plus grand taux d’occupation de celles les plus éloignées. Afin d’optimiser la bande passante du SciFi, 2 types de firmware TELL40 ont été développés pour gérer le Widebus(112-bit frames) :- TELL40-16liens avec un format de données nommé fixe-variable pour les régions à haute occupation qui permet une acquisition maximum de 16 clusters par lien,

- TELL40-40liens avec un format de données nommé fixe-fixe pour les autres qui permet une acquisition maximum de 10 clusters par lien.

La figure suivante montre le positionnement des TELL40s pour une C-frame.

- TELL40 configuration

- source : EDMS ID 1904563

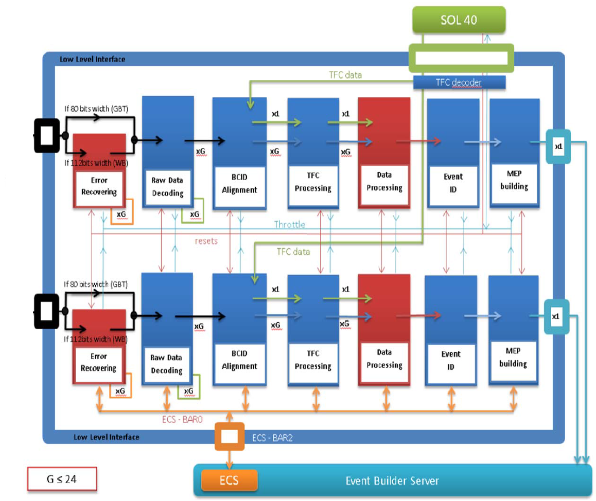

- Architecture du firmware

La version TELL40 du FPGA peut supporter jusqu’à 48 liens de données en entrée, séparer en 2 flots de 24 liens de données. Elle permet d’acquérir des données au format GBT-Widebus : (112bits) provenant des cartes Front End, de les formater et de les transférer vers un serveur de données via 2 interfaces PCI_express.

- Architecture firmware TELL40

- source : EDMS ID 1904563

-* Le firmware est constitué de différents modules de traitement permettant de décoder les données GBT, d’aligner tous les liens en fonction du BCID, vérifier la corrélation des données attendues par rapport au TFC, les formater au format spécifique SciFi et les transmettre sur l’interface PCI_express à travers le MEP.

- Module « Data processing »

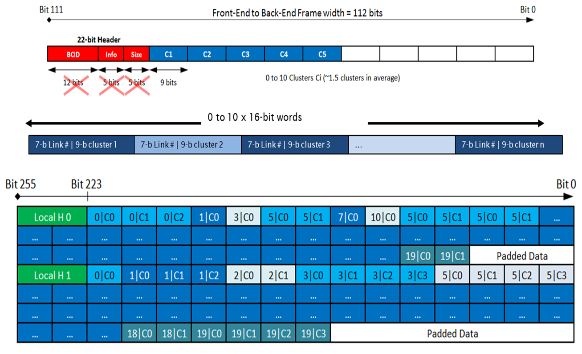

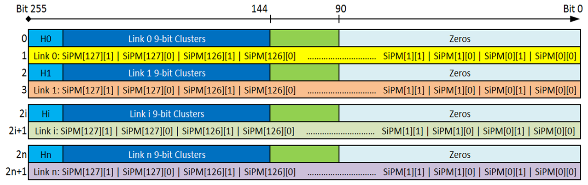

-*Le module « Data Processing » est le processus de formatage de données. C’est la partie du firmware TELL40 qui s’adapte au format spécifique de données du détecteur.

Il formate les données d’entrée de l’ensemble des liens afin d’obtenir une série de trame de 256 bits transmise à 250 MHz via le bus PCI-EXPRESS.

Dans le cas du SciFi, les données en sortie de module sont FTCluster, FTNZS et FTCalibration.- FTCluster

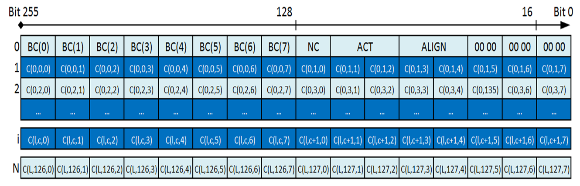

Le format FTCluster contient les données « physics zero‐suppressed » (Cluster), c’est à dire une entête de 32 bits et la liste de N clusters issus de tous les liens d’entrée.

- FTCluster

- Clusters fragment

- source : EDMS ID 1904563

-

- FTNZS

Le format FTNZS contient les données NZS (Non zero suppressed), lesquels sont généralement générés durant la calibration pour caractériser les carte front end. Il contient également les données clusters.

- FTNZS

- NZS fragment

- source : EDMS ID 1904563

-

- FTcalibration

Le module « data processing » intègre une liste de compteur embarqué afin d’accélérer la procédure de calibration en calculant les histogrammes des channels à la volée. Le format FTcalibration de mettre en forme le résultat des compteurs embarqués.

- FTcalibration

- counter fragment

- source : EDMS ID 1904563

-

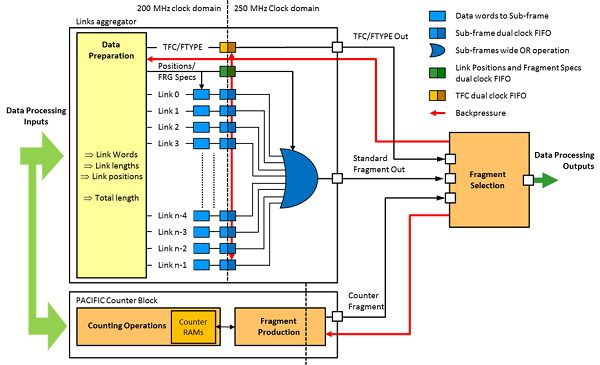

- Implémentation du firmware

le module « data processing » intègre 2 processus qui fonctionnent en parallèle ; le processus d’agrégation de liens qui formate les données provenant du Front end et le processus PACIFIC qui calcule les histogrammes. Il intègre également un sélecteur qui gère l’affection des fragments de sortie vers un bus de 256bits.

- Implémentation du firmware

- Structure du module Data Processing

- Source : EDMS ID 1904563

Le processus d’agrégation génère des fragments de 256bits ; lesquels sont produits à base d’une table de vecteur 16-bit de taille variable, pour chaque évènement valide en entrée.

Pour chaque lien, on détermine le nombre de données à transmettre et la position du premier vecteur dans la table de vecteurs 16-bit. Ensuite, on construit une sous-trame que l’on vient stocker dans une FIFO. En parallèle, on stocke dans 2 FIFOs les informations TFC, la spécification du fragment en construction et sa position dans la table.

Pour finir, à l’aide d’un « OU » logique, on forme les fragments de sortie de 256bit en sérialisant la FIFO d’informations TFC, la FIFO de spécification et la FIFOs de chaque lien qui a contribué à l’évènement à transférer.

-

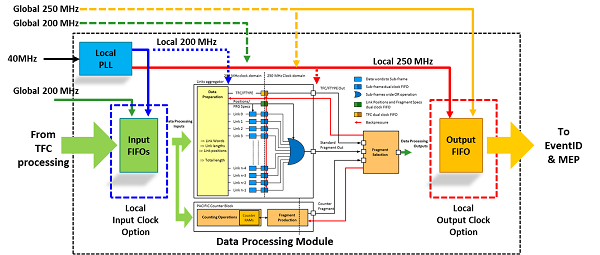

- Distribution d’horloge

Le firmware fonctionne sur 2 domaines d’horloges : 200 Mhz pour acquérir les données d’entrée et 250 MHz pour générer les fragments de sorties.

- Distribution d’horloge

- Distribution d’horloge dans le module « data processing »

- source : EDMS ID 1904563

« »

Interface de contrôle WinCC

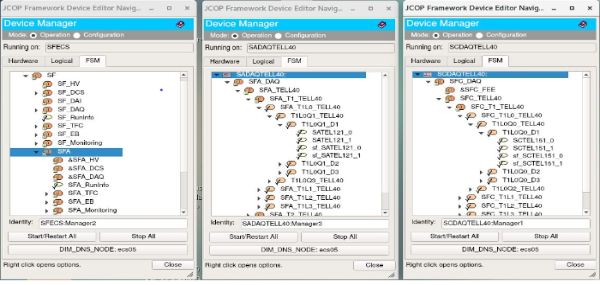

La collaboration LHCb utilise WinCC OA (et un framework développé par le CERN, JCOP) comme système de contrôle et d’acquisition de données (SCADA) de l’expérience.

Le LPNHE a produit des développements spécifiques pour le déploiement des cartes TELL40 du sous-détecteur SciFi permettant d’assurer le contrôle, le monitoring, et le suivi de la qualité des données produites par ces cartes.

L’architecture logicielle du système est basée sur une structure hiérarchisée, permettant de piloter les divers élements de l’expérience par l’intermédiaire de machine d’états. L’image suivante est un screenshot de l’arborescence de la machine d’états TELL40 pour la partition A et C.

Voir en ligne : Video de l’installation de C-Frame dans la caverne

Dans la même rubrique :